반도체 시장의 혁신,

p형 반도체 소재의 등장

플렉시블전자소자연구실 남수지, 최경희 선임연구원

집에서도 4K UHD 고해상도 영화, 드라마를 즐길 수 있는 시대가 됐다.

더 선명하고, 더 좋은 화질을 향한 디스플레이 기술의 계속되는 발전이 있었기에 가능했다.

이 기술의 중심에는 박막 트랜지스터(TFT)가 있다.

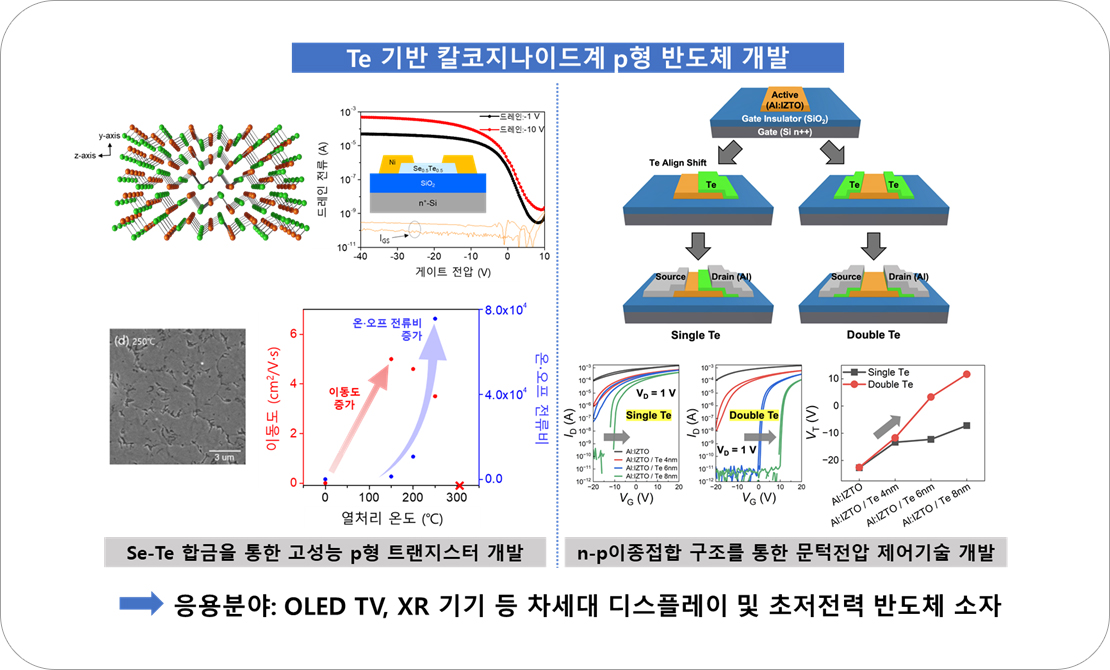

ETRI는 p형 셀레늄-텔루륨(Se-Te) 합금 트랜지스터와 n형 트랜지스터 문턱전압 조절 기술을 개발했다.

남수지, 최경희 선임연구원은 해당 기술이 차세대 초고화질 디스플레이 구현에 도움을 줄 수 있을 것이라 설명했다.

본인 소개와 이번에 개발하신 p형 Se-Te 합금 트랜지스터 기술과 n형 트랜지스터 문턱전압 조절 기술을 소개해 주세요.

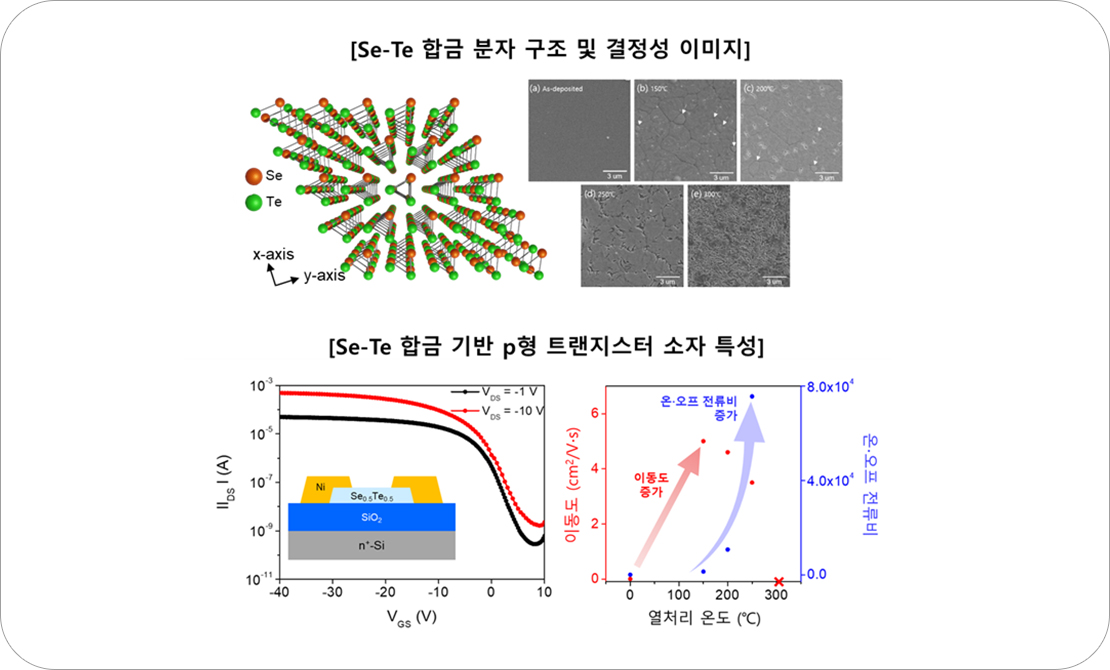

최경희 선임연구원안녕하세요. 초실감메타버스연구소 실감소자연구본부 플렉시블전자소자연구실의 최경희 선임연구원입니다. 이번에 개발한 p형 박막 트랜지스터(TFT)*는 상온에서 펄스 레이저를 사용해 60nm 두께의 Se-Te 합금 채널층을 증착해 제작됐어요. 본 연구에서 사용한 Se-Te 합금 채널층은 기존에 보고된 p형 Te 채널층에 비해 결정화 온도가 높고, 밴드갭이 큰 특성이 있어요. 그래서 Se-Te 합금 채널층으로 TFT를 제작하고 250℃ 저온**에서 열처리해 이동도 3, 온·오프 전류비 105의 준수한 특성의 p형 TFT를 제작했어요. 그리고 p형 Se-Te TFT를 n형 Al:InZnSnO TFT와 연결해 CMOS 인버터***를 제작하고 특성을 확인해 로직 회로에서 사용 가능성을 확인했어요.

* 박막 트랜지스터(Thin Film Transistor, TFT): 유리 기판 등의 절연 물체 위에 화학 증착법(CVD)으로 트랜지스터를 형성하는 것.(출처: TTA 정보통신용어사전)

** 보통 TFT 공정은 350℃~400℃ 미만의 고온 공정으로 진행된다.

*** CMOS(complementary metal-oxide semiconductor) 인버터: n형 TFT 하나와 p형 TFT 하나를 연결해 구성하는 인버터로, 로직 회로를 구성하는 가장 기본적인 소자다.

본 연구 내용 요약: Te 기반의 칼코지나이드계 p형 반도체 소재의 응용분야

남수지 선임연구원안녕하세요. 플렉시블전자소자연구실의 남수지 선임연구원입니다. n형 트랜지스터 문턱전압 조절 기술은 말 그대로 문턱전압을 정밀하게 조절하는 기술이에요. 문턱전압이란 트랜지스터에서 전류가 흐르기 시작하는 데 필요한 최소한의 전기 신호예요. 디스플레이 백플레인* 소자나 반도체 소자의 기본이 되는 트랜지스터에서 문턱전압을 조절하는 것은 매우 중요해요. 문턱전압이 너무 높으면 소자가 잘 켜지지 않고, 너무 낮으면 불필요한 전류가 흘러서 전력을 낭비하게 되죠. 그래서 문턱전압을 적절한 값으로 유지하는 것이 중요해요. 이번에 개발된 기술은 디스플레이나 반도체 소자의 성능, 전력 효율성과 안정성 등을 향상하기 위해 문턱전압을 체계적으로 조절하는 기술이에요.

* 백플레인(Backplane): 디스플레이를 구동시키는 회로 소자가 장착된 뒤판을 의미한다.

남수지 선임연구원

고해상도 디스플레이에 240Hz 이상의 주사율이 요구되면서 p형 반도체 개발에 대한 관심이 커지고 있습니다. 그 이유가 무엇인가요?

남수지 선임연구원최근 중소형 디스플레이와 더불어 대형 디스플레이에서도 고해상도와 고주사율 특성이 요구되고 있어요. 중소형 디스플레이에서는 LTPS(Low-Temperature Polycrystalline Silicon)* TFT 또는 LTPS TFT와 산화물 TFT로 구성된 LTPO(Low-Temperature Polycrystalline Oxide)**를 패널 또는 주변 회로에서 사용하고 있지만 대면적 공정에 한계가 있어요. 또한 LTPS TFT와 산화물 TFT 간의 공정의 상이성으로 인해 복잡한 공정 과정이 필요해서 대형 디스플레이에 적용하기엔 어려움이 있고요.

현재 대형 디스플레이에서는 대면적 공정이 가능한 n형 산화물 TFT를 패널에서 주로 사용하고 있어요. 하지만 전류 구동의 안전성과 주변 회로에 낮은 정적 소비 전력, 단순한 회로 구성, 낮은 노이즈 영향 등의 장점이 있는 CMOS를 적용하기 위해서는 성능이 우수하고 공정이 단순하며, 대면적 공정이 가능한 p형 반도체 소재와 공정 개발이 필수적이라고 볼 수 있죠.

* LTPS(Low-Temperature Polycrystalline Silicon): 저온 다결정 실리콘으로 비결정 실리콘에 레이저를 조사해서 다결정 실리콘으로 만들어 채널로 사용하는 TFT이다. 전자 이동 속도가 빨라 선명한 디스플레이를 구현한다는 특징이 있다.

** LTPO(Low-Temperature Polycrystalline Oxide): 저온 다결정 산화물로 Apple이 개발한 TFT 기술이다. 빠른 전자이동이 특징인 LTPS와 누설전류가 작은 Oxide를 활용해 전력 효율을 개선한 기술이다.

Se-Te 합금의 분자 구조 및 결정성 이미지와 이를 기반으로 한 p형 트랜지스터 소자 특성 결과

새롭게 개발하신 p형 반도체는 Te에 Se를 첨가했습니다. 이 기술의 특징과 장점은 무엇일까요?

최경희 선임연구원Te의 밴드갭은 두께에 따라 0.31(벌크)~1.26eV(단층)이고, Te의 결정화 온도는 –10℃ 이하예요. Te을 채널층으로 사용해 성능이 우수한 p형 트랜지스터를 제작하기 위해서는 10nm 이하의 얇은 두께로 증착해 Te 박막의 밴드갭을 증가시켜야 해요. 또한 –80℃의 저온에서 증착해 Te의 결정 크기를 크게 하거나, 상온에서 증착한 후 Te 채널층 위에 패시베이션층을 증착해 Te의 산화를 막고 결정성을 높이거나, Te 채널층을 상온에서 증착하기 전에 표면 처리를 해 나노 크기 Te의 결정 방향을 조절해야 하죠.

Se-Te 합금층을 채널층으로 사용하면 결정 구조 변화 없이 채널층의 밴드갭이 증가해 10nm 이상의 두께에서도 온·오프 전류비가 확보되는 p형 트랜지스터 제작이 가능해져요. 또한 Te 대비 Se-Te 합금층은 높은 결정화 온도를 가지고 있어서 상온에서 비결정으로 증착한 후 후속 열처리를 통해 합금층의 결정성을 높여 p형 트랜지스터의 이동도와 신뢰성을 높일 수 있죠. 열처리 과정에서 Se-Te 합금층 표면에 Te의 산화에 의해 TeO2 층이 생겨 추가 패시베이션층 증착 없이도 열처리 과정에서 발생할 수 있는 합급층 하부층의 산화와 기화 또는 증발을 막아줄 수 있어요.

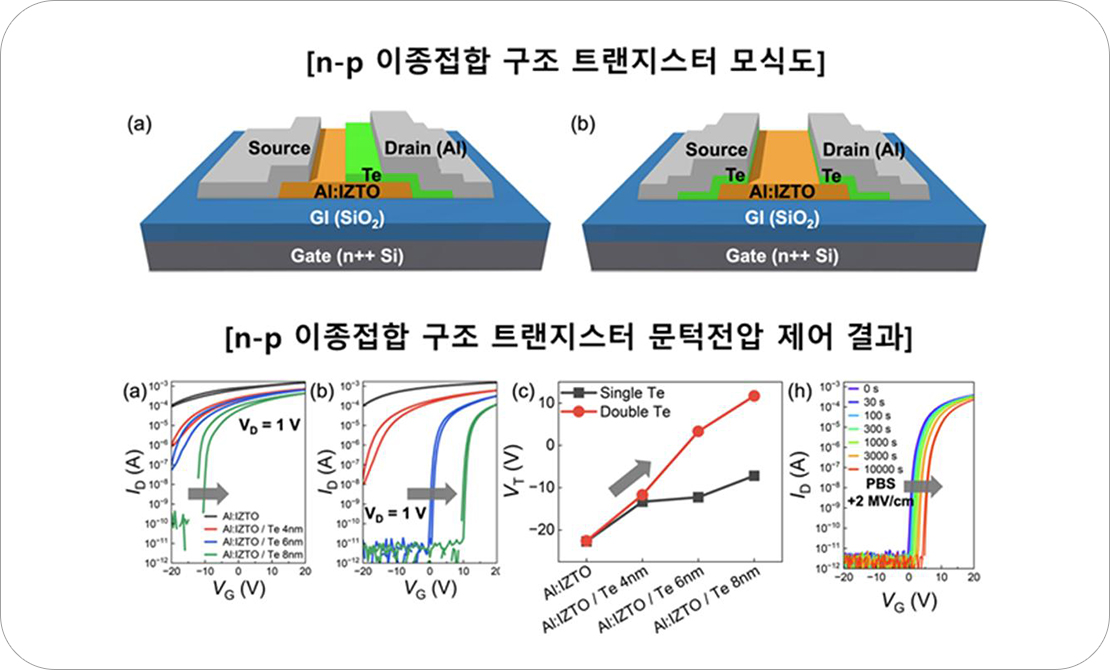

n형 산화물 반도체 위에 칼코지나이드계 p형 Te을 이종접합으로 도입한 소자의 모식도 및 이를 기반으로 트랜지스터의 문턱전압을 제어한 소자 특성 결과

p형 반도체와 n형 반도체의 이종접합 구조를 통해 패시베이션 층 없이도 n형 트랜지스터의 문턱전압을 조절할 수 있게 됐습니다. 이에 대해 설명해 주세요.

남수지 선임연구원지금까지 디스플레이에서는 트랜지스터의 문턱전압을 조절하는 방법으로 주로 게이트 절연층이나 반도체 박막 두께를 변화시키거나, 이중 게이트 전극을 사용하는 방법, 반도체 내부에 도핑 농도를 조절하는 방법 등이 주로 사용되어 왔어요.

이번 연구에서는 일반적으로 사용되는 n형 산화물 반도체층 위에 Te라고 하는 p형 반도체를 얇게 이종접합으로 증착하는 방법을 사용했어요. n형 산화물 반도체의 전하 이동을 체계적으로 제어하는 방법을 통해 문턱전압을 조절하는 방법을 처음으로 제시한 거죠. 그래서 n형 산화물 반도체에 필수적이었던 패시베이션 층 없이도 우수한 전기적 안정성을 갖는 소자를 제작할 수 있게 됐어요.

패시베이션 층은 소자를 외부의 환경으로부터 보호하는 박막이에요. 일반적으로 패시베이션 층이 없는 경우 외부 바이어스를 걸어주었을 때, n형 산화물 반도체 트랜지스터의 문턱전압이 크게 변하게 되는데요. 이번 연구에서 p형 반도체를 n형 반도체 위에 얇게 형성시켜 n형 반도체의 전자 흐름을 제어하게 했어요. 이렇게 해서 패시베이션 층 없이도 안정적인 문턱전압을 가질 수 있게 된 거죠.

두 기술이 앞으로 어떤 분야에 사용될 수 있을까요?

남수지 선임연구원이번 연구에서 개발한 p형 TFT를 사용해 제작한 CMOS로 OLED TV를 제작할 수 있어요. 기존 n형 TFT와 개발한 p형 TFT를 적층해 높은 집적도를 가지는 초고해상도 XR 기기와 같은 차세대 디스플레이 구현에도 사용될 수 있고요.

최경희 선임연구원

최경희 선임연구원이번 성과는 디스플레이뿐만 아니라 반도체 산업에서도 활용될 수 있어요. 현재 세계 유수의 반도체 기업들이 반도체의 집적도를 증가시키는 미세공정을 개발하고 있지만, 많은 전문가가 반도체 집적도 증가가 한계에 달했다고 분석하고 있어요.

그래서 최근에는 여러 개의 반도체 칩을 쌓는 적층 방식이 활용되고 있어요. 실리콘 관통전극(TSV)은 가장 대표적인 적층 방식인데요. 여러 개의 웨이퍼를 쌓고 구멍을 뚫어 전기적으로 연결하는 방법이에요. 기판 위의 공간 활용도를 높이고, 소비전력을 줄일 수 있다는 장점이 있죠. 하지만 큰 공정 비용과 낮은 수율 등 극복해야 할 문제점도 많아요.

TSV의 한계를 극복하기 위해, 최근에는 여러 개의 웨이퍼를 적층하는 대신 하나의 웨이퍼 위에 소재를 층층이 쌓아 올리는 모놀리틱 3D(M3D) 방식이 주목받고 있어요. 하지만 아직 상용화 단계에는 이르지 못했죠. 그러나 이번에 개발한 n형 산화물 반도체와 Te 기반의 p형 반도체 이종접합 박막 트랜지스터 및 p형 반도체 소자는 300℃ 이하의 공정으로도 안정적으로 작동해 M3D 상용화에 한 발짝 더 다가섰다고 할 수 있어요.

연구하시면서 가장 큰 어려움은 무엇이었나요? 있었다면 어떻게 극복하셨나요?

최경희 선임연구원연구가 계획하는 대로 결과가 나오는 것이 아니여서 원하지 않는 실험 결과가 나오거나 계획과 다른 방향으로 흘러갈 때면 방황하게 될 때가 있었어요. 그때가 가장 어려운 시기였죠. 그럴 때면 다시 한번 목표를 설정하고 큰 그림을 그리며 문제점을 찾아서 하나하나 해결해 나가면서 어려움을 극복했어요.

남수지 선임연구원새로운 물질이나 구조를 실험해 의미 있는 결과를 얻기 위해서는 여러 장비에서 다양한 조건, 물질, 구조로 여러 번 실험해야 했어요. 이 과정에서 개인의 노력과 인내도 필요했지만, 이번 연구 결과를 얻는 데까지 과제원들의 조언과 지지가 큰 도움이 됐어요.

박사님과 플렉시블전자소자연구실의 추후 연구 계획과 포부를 듣고 싶습니다.

최경희 선임연구원디스플레이와 반도체는 우리나라의 주력산업이에요. 지속적으로 발전하고 혁신을 이뤄나갈 분야죠. 그래서 실리콘이 아닌 비 실리콘 반도체 소재의 개발은 필수적이에요. 특히 n형 반도체에 비해 성능이 떨어지는 p형 반도체 개발은 꼭 필요해요. 추후에는 대면적 p형 TFT 어레이와 CMOS 로직 회로를 제작해 고해상도, 저전력 디스플레이 백플레인 및 DRAM 메모리 연구 등에 폭넓게 응용해 보고 싶어요.

이전 기사보기

이전 기사보기